HAMAMATSU, JAPAN

200809-

SY

011926

SERVICE MANUAL

’08.09

SPECIFICATIONS ..............................................4/6

PANEL LAYOUT ......................................8

CIRCUIT BOARD LAYOUT .................9

WIRING ..............................................................9

DISASSEMBLY PROCEDURE ............................10

LSI PIN DESCRIPTION .............................14

IC BLOCK DIAGRAM ..................................21

CIRCUIT BOARDS .......................................23

FIRMWARE VERSION CHECK

..................................34/35

BACKUP ..................................................36/38

.........................................39

FACTORY SET ..................................40

TEST PROGRAM .............................41/53

BOOT SEQUENCE

PARTS LIST

BLOCK DIAGRAM

CIRCUIT DIAGRAM

CONTENTS

/

MR816CSX

Steinberg and Cubase are the registered trademarks of Steinberg Media Technologies GmbH.

MR816CSX/MR816X

2

WARNING

Components having special characteristics are marked and must be replaced with parts having specifi cation equal to those

originally installed.

WARNING:

This product contains chemicals known to the State of California to cause cancer, or birth defects or other reproductive harm.

DO NOT PLACE SOLDER, ELECTRICAL/ELECTRONIC OR PLASTIC COMPONENTS IN YOUR MOUTH FOR ANY REASON WHAT SO EVER!

Avoid prolonged, unprotected contact between solder and your skin! When soldering, do not inhale solder fumes or expose eyes to solder/

flux vapor!

If you come in contact with solder or components located inside the enclosure of this product, wash your hands before handling food.

IMPORTANT NOTICE

This manual has been provided for the use of authorized Yamaha Retailers and their service personnel. It has been assumed that basic

service procedures inherent to the industry, and more specifically Yamaha Products, are already known and understood by the users,

and have therefore not been restated.

WARNING :

Static discharges can destroy expensive components. Discharge any static electricity your body may have accumulated

by grounding yourself to the ground bus in the unit (heavy gauge black wires connect to this bus.)

IMPORTANT :

Turn the unit OFF during disassembly and parts replacement. Recheck all work before you apply power to the unit.

IMPORTANT NOTICE FOR THE UNITED KINGDOM

Connecting the Plug and Cord

IMPORTANT. The wires in this mains lead are coloured in accordance with the following code:

BLUE : NEUTRAL

BROWN : LIVE

As the colours of the wires in the mains lead of this apparatus may not correspond with the coloured markings identifying the terminals in

your plug proceed as follows:

The wire which is coloured BLUE must be connected to the terminal which is marked with the letter N or coloured BLACK.

The wire which is coloured BROWN must be connected to the terminal which is marked with the letter L or coloured RED.

Making sure that neither core is connected to the earth terminal of the three pin plug.

• This applies only to users in the United Kingdom. (2 wires)

3

MR816CSX/MR816X

SAVING DATA

Saving and backing up your data

• Storing the settings to internal memory of the MR816 CSX/MR816 X must be performed from the MR Editor on the computer.

If you use the MR816 CSX/MR816 X with MR Editor, you can store the settings to internal memory by storing the settings as a

Scene or recalling the Scene on the MR Editor. Also, you can save 20 Scenes as an Editor fi le to the computer. If you use the

MR816 CSX/MR816 X with Cubase, you cannot store the settings to internal memory of the MR816 CSX/MR816 X. Save the

settings as a project fi le to the computer. You should also save your Project fi les or Editor fi les onto external media as backup

to avoid the loss of important data due to equipment malfunction or improper operation.

• If you want to store the settings edited on the MR816 CSX/MR816 X without a computer, launch the MR Editor with the

computer and MR connected, then perform the Scene Store operation. This operation will store the settings to the internal

memory of the MR816 CSX/MR816 X and the MR Editor as a Scene.

Be sure to

perform it

MR816CSX/MR816X

4

SPECIFICATIONS

Electrical Characteristics

Sample Rate

Internal 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz

External 44.1kHz, 48kHz, 88.2kHz, 96kHz (± 0.1%)

Total Harmonic Distortion GAIN: Minimum 0.004% or less (1 kHz @ +18 dB, into 600 Ω)

Frequency Response

(CH IN to LINE OUT)

fs = 48 kHz 20 Hz−20 kHz, +1, -3 dB @ +4 dB, into 600 Ω

fs = 96 kHz 20 Hz−40 kHz, +1, -3 dB @ +4 dB, into 600 Ω

Dynamic Range

(SN ratio at the maximum level)

104 dB, DA converter (LINE OUT)

97 dB, AD + DA (to LINE OUT)

Hum & Noise

(20 Hz−20 kHz)

Rs = 150 Ω

-118 dB, Equivalent input noise

-86 dB, Residual output noise, Output fader: Minimum

GAIN: Maximum

-86 dB (90 dB SN), LINE OUT

PAD: OFF

Output channel fader: Nominal, All Input channel faders: Minimum

GAIN: -60 dB

-53 dB (57 dB SN), LINE OUT

PAD: OFF

Output channel fader: Nominal, Input channel fader (one channel): Nominal

Maximum Voltage Gain 84 dB, CH1 − 8 to LINE OUT

Crosstalk @ 1 kHz

GAIN: Minimum

Adjacent Input

-85 dB, CH1 − 8

Input and Output Specifi cations

Analog Input Type

Input Level

Nominal Level Maximum Level Input Impedance

MIC/LINE/HI-Z jack 1,

MIC/LINE jack 2 and MIC/LINE IN

jacks 3 − 8 (CH1 − 8)

XLR type balanced,

+48 V Phantom powered

-60 dBu to +10 dBu +24 dBu 3.5 kΩ

INSERT I/O jack 1 and 2 (INSERT IN) TRS phone type, unbalanced 0 dBu +14 dBu 10 kΩ

Analog Input Type

Output Level

Nominal Level Maximum Level Input Impedance

OUTPUT jacks 1 − 8

(Line Output)

TRS phone type, balanced +4 dBu +18 dBu 600 Ω

INSERT I/O jack 1 and 2

(INSERT OUT)

TRS phone type, unbalanced +4 dBu +18 dBu 10 kΩ

Headphone jacks 1 and 2

(Monitor 1/2)

TRS phone type, unbalanced

4 mW + 4 mW 25 mW + 25 mW 8 Ω

12 mW + 12 mW 75 mW + 75 mW 40 Ω

General Specifi cations

Power Requirements 40 W (PA-30)

Dimensions (H x D x W) 44 x 305 x 480 mm

Net Weight 3.2 kg

Operating Free-air Temperature Range +5 − +35

Included Accessories

AC power adaptor (PA-30 or equivalent)

DVD-ROM (Cubase AI 4)

CD-ROM (TOOLS for MR)

Getting Started manual (printed booklet)

IEEE1394 cable

Rubber stoppers x 4

5

MR816CSX/MR816X

Functions

Input Channels 1 − 8

Analog Input

MIC Preamp Discrete Class-A MIC preamp (Inverted Darlington Circuitry)

[+48 V] button

(Phantom Power switch)

+48 V DC

[PAD] button 0/26 dB

Gain knob 44 dB variable (-60 dB to -16 dB)

Phase Normal/Reversed (controlled via a computer)

High Pass Filter

OFF/80 Hz (-12 dB/oct.)

Controlled via a computer

[HI-Z] switch On/off (for channel 1), Input impedance: 500 kΩ

AD converter 24 bit linear, Enhanced dual-bit delta-sigma conversion

[SIG/PEAK] lamp

-3 dB or mode (red), -40 db − -3 dB (green) (when the clipping point of the

signal is assumed to be 0 dB)

Output Channels 1 − 8

Analog Output

Level Control

Multi Function Encoder knob control (for all the channels 1 − 8)

Software control (for each of the channels 1 − 8)

DA converter 24 bit linear, 128 times oversampling Advanced multi-bit delta/sigma conversion

Headphone jacks

1 and 2

Level Control Multi Function Encoder knob control

Maximum Output Level 25 mW (@ 8 Ω)/75 mW (@ 40 Ω)

IEEE1394 jack

Audio interface 16-ch input/16-ch output

European models

Purchaser/user Information specifi ed in EN55103-1 and EN55103-2.

Inrush current: 2.0 A (MR816 CSX), 2.0 A (MR816 X)

Conforms to environments: E1, E2, E3, E4

MR816CSX/MR816X

6

7

MR816CSX/MR816X

MR816CSX/MR816X

8

PANEL LAYOUT

q [HI-Z] switch

w [MIC/LINE/HI-Z] jack 1 (analog input jack 1) and

[MIC/LINE] jack 2 (analog input jack 2)

e [QUICK CONNECT] buttons (with LED lamps)

r [SIG/PEAK] lamps

t Gain knobs 1 – 8

y [+48V] button (phantom power button; with

LED lamps)

u [PAD] button (with LED lamps)

i [ASSIGN] lamps

(The [MORPH] lamp is only MR816CSX.)

o Word Clock Source lamps

!0 Sample Rate lamps

!1 Multi Function encoder knobs 1 and 2

(with LED lamps)

!2 Headphone jacks 1 and 2

!3 [STANDBY/ON] switch

006*)

/4 4112-

MR816CSX only

q [AC ADAPTOR IN] jack

w [S/PDIF IN/OUT] jack

e [OPTICAL IN/OUT] jack

r IEEE1394 jacks 1 and 2

t [WCLK IN/OUT] jacks (wordclock in/out jack)

y [OUTPUT] jacks 1 – 8 (analog output jacks 1 – 8)

u [MIC/LINE INPUT] jacks 3 – 8

(analog input jacks 3 – 8)

i [INSERT I/O] jacks 1 and 2

401 6 2 *

/)

• Front panel

• Rear panel

q

w

e

r

t

y

u

i

o

!0

!1

!2

!3

q

w

e

r

t

y

u

i

9

MR816CSX/MR816X

AC

PN

HP

DM

JK

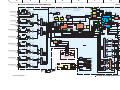

CIRCUIT BOARD LAYOUT

WIRING

JK

PN

HP

DM

AC

CN301

(12P)

CN901

(12P)

CN851

(2P)

CN104

(4P)

CN850

(2P)

CN112 (30P)

CN101 (30P)

CN102 (30P)

CN111 (30P)

CN601

(6P)

CN651

(7P)

CN701

(6P)

CN602

(6P)

CN652

(7P)

CN702

(6P)

CN201

(8P)

CN800

(8P)

CN102

(5P)

CN103

(4P)

CN101

(3P)

CN151

(4P)

PSW wiring assembly

AC wiring assembly

MR816CSX/MR816X

10

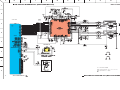

DISASSEMBLY PROCEDURE

Fig. 1

Photo 1

Precautions

* Notes on Flat Cable

Contacts are visible from the back. Pay attention not to

insert and install the cable to the connector inversely.

(Photo 1)

Front Side Back Side

We recommend you use the dedicated driver bit from HIOS

Inc. (model number: THS6X-30-75) when you remove

screws marked [118], [148A], [148B] or [148C].

[148A] x 2

[148A] x 2

[148A] x 3

[148A]

x 3

[118]

[118]

[148B] x 3

[148C] x 3

[144] [142] [142] [142]

[144]

[144][172]

• Rear view

TOP COVER

CONNECTOR COVER

TOP COVER

FRONT PANEL

FABRIC GASKET

FABRIC GASKET

[118]: SCREW RAMI #S 3.0X6 MFZN2B3 (WN110000)

[142]: BIND HEAD P-TIGHT SCREW 3.0X8 MFZN2B3 (WF266600)

[144]: BIND HEAD TAPPING SCREW-S 3.0X6 MFZN2B3 (WE87780R)

[148A], [148B], [148C]: SCREW RAMI #S 3.0X6 MFZN2B3 (WN110000)

[172]: BIND HEAD TAPPING SCREW-S 3.0X6 MFZN2B3 (WE87780R)

11

MR816CSX/MR816X

1. Top Cover (Time required: About 6 minutes)

1-1 Remove the following screws and slide the top cover

toward the rear side to remove it. (Fig. 1)

[142]: 16 pcs.

[144]: 8 pcs.

[148A]: 10 pcs.

[148B]: 3 pcs.

[172]: 1 pc.

* The connector cover will be removed together when

the screw marked [172] is removed. Take care not to

lose it. (Fig. 1)

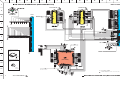

2. JK Circuit Board

(Time required: About 7 minutes)

2-1 Remove the top cover. (See procedure 1.)

2-2 Unhook the three (3) hooks of the PCB space holder.

The JK circuit board can then be removed. (Photo 2)

Fig. 2

Photo 2

JK

PCB SPACE HOLDER

[56]

[56]

[52A]

[52B]

[22A]

[22B]

• Top view

WIRING ASS'Y, AC

WIRING ASS'Y, AC

CORD HOLDER X 4

FABRIC GASKET

DM

AC

12

PCB SPACE HOLDER

[22A], [22B]: BIND HEAD TAPPING SCREW-S 3.0X6 MFZN2B3 (WE87780R)

[52A], [52B]: BIND HEAD TAPPING SCREW-S 3.0X6 MFZN2B3 (WE87780R)

[56]: BIND HEAD TAPPING SCREW-S 4.0X8 MFZN2B3 (WE99480R)

MR816CSX/MR816X

12

Fig. 3

3. AC Circuit Board and Wiring Ass'y, AC

(Time required: About 7 minutes)

3-1 Remove the top cover. (See procedure 1.)

3-2 Remove the two (2) screws marked [52A], the screw

marked [52B] tightened together with the cord holder,

and the screw marked [56]. The AC circuit board and

wiring ass'y, AC can then be removed. (Fig. 2)

* The fabric gasket attached to the wiring ass'y, AC is

not part of the wiring ass'y, AC. (Fig. 2)

4. Front Panel (Time required: About 8 minutes)

4-1 Remove the eight (8) knobs marked [A] and two (2)

knobs marked [B]. (Fig. 3)

4-2 Remove the two (2) screws marked [118], three (3)

screws marked [148B] and three (3) screws marked

[148C]. The front panel can then be removed. (Fig. 1)

* The lenses attached to the rear side of the front

panel is not part of the front panel. (Fig. 3)

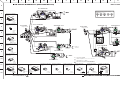

5. PN Circuit Board, HP Circuit Board and

Wiring Ass'y, PSW

5-1 Remove the top cover. (See procedure 1.)

5-2 Remove the front panel. (See procedure 4.)

5-3

PN Circuit Board (Time required: About 11 minutes)

5-3-1 Remove the four (4) screws marked [104]. The two (2)

combo angles can then be removed. (Fig. 4)

5-3-2 Remove the four (4) screws marked [46] and eight (8)

hexagonal nuts marked [48]. The PN circuit board can

then be removed. (Fig. 4)

5-3-3 Remove the eight (8) buttons marked [C] and two (2)

buttons marked [D] from the PN circuit board. (Fig. 4)

* The buttons marked [C] and [D] are not part of the

PN circuit board. When replacing the PN circuit

board, remove the buttons and attach them to the

new PN circuit board.

* When installing the PN circuit board, tighten the

screws 1 and 2 shown in Fig. 4 in numerical order

and then tighten the other screws. (Fig. 4)

5-4 HP Circuit Board and Wiring Ass'y, PSW

(Time required: About 10 minutes)

5-4-1

Remove the screw marked [62] and remove the HP

circuit board and wiring ass’y PSW by sliding them

toward the front side. (Fig. 4, Fig. 5)

[A]

Lens

Lens

[B]

• Front view

• Rear view

FRONT PANEL

FRONT PANEL

13

MR816CSX/MR816X

Fig. 4

Fig. 5

6. DM Circuit Board

(Time required: About 11 minutes)

6-1 Remove the top cover. (See procedure 1.)

6-2 Remove the JK circuit board. (See procedure 2.)

6-3 Remove the front panel. (See procedure 4.)

6-4 Remove the four (4) screws marked [104]. The two (2)

combo angles can then be removed. (Fig. 4)

6-5

Remove the eight (8) hexagonal nuts marked [48]. (Fig. 4)

6-6 Remove the three (3) screws marked [22A] tightened

together with the cord holder and seven (7) screws

marked [22B]. The DM circuit board can then be

removed. (Fig. 2)

* The fabric gasket attached to the DM circuit board is

not part of the DM circuit board. (Fig. 1)

* The PCB space holder are not part of the DM circuit

board. When replacing the DM circuit board, remove

the PCB space holder and attach them to the new

DM circuit board.(Fig. 2)

* When installing the DM circuit board, tighten the

screws 1 and 2 shown in Fig. 2 in numerical order

and then tighten the other screws. (Fig. 2)

5-4-2 Remove the wiring ass'y, PSW from the JK switch

angle. (Fig. 5)

5-4-3 Remove the two (2) angle brackets, U. The HP circuit

board can then be removed. (Fig. 5)

• Front view

[104] [104]

[48]

[C] [C] [D]

[46]

[62]

COMBO ANGLE

[48]

[48]

[46]

WIRING ASS'Y, PSW

PN

1

2

[46]: BIND HEAD TAPPING SCREW-S 3.0X6 MFZN2B3 (WE87780R)

[48]: HEXAGONAL NUT 9.0 MFNI33 (V243140R)

[62]: BIND HEAD TAPPING SCREW-S 3.0X6 MFZN2B3 (WE87780R)

[104]: FLAT HEAD TAPPING SCREW-B 3.0X8 MFZN2B3 (WF266800)

[62]

WIRING ASS'Y, PSW

WIRING ASS'Y, PSW

JK SWITCH ANGLE

JK SWITCH ANGLE

ANGLE BRACKET, U

ANGLE BRACKET, U

HP

HP

[62]: BIND HEAD TAPPING SCREW-S 3.0X6 MFZN2B3 (WE87780R)

MR816CSX/MR816X

14

LSI PIN DESCRIPTION LSI

1394AV-L (X6893A00) DICEII .....................................................................................................16

17

AK4358VQ (X4289A00) DAC (Digital to Analog Converter) ................................................................20

AK5385BVF-E2 (X5364B00) ADC (Analog to Digital Converter) ........................................................19

EP1C3T100C8N (X5691A00) FPGA....................................................................................................14

MB87S1280 (X6363A00) SSP1 (MAIN/SUB) ......................................................................................18

MN101C027YB (XS71120R) CPU .......................................................................................................15

S1L50553F21Y000 (X4195A0R) MCI (Gate Array) .............................................................................19

TSB41AB2PAP (XZ665A00) PHY .......................................................................................................15

YAC523-VZ (X4325A00) EVR2 (Electric Variable Resistance 2) .........................................................20

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

IO

IO

IO

IO

IO

nCSO

DATA0

nCONFIG

VCCA_PLL1

CLK0

GNDA_PLL1

nCEO

nCE

MSEL0

MSEL1

DCLK

ASDO

VCCIO1

GND

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

GND

VCCIO4

GND

VCCINT

IO

IO

IO

IO

IO

IO

IO

IO

IO

GND

VCCINT

GND

VCCIO4

IO

IO

IO

I/O

I/O

I/O

I/O

I/O

O

I

I

-

I

-

O

I

I

I

I/O

O

-

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

-

I/O

-

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

-

-

-

I/O

I/O

I/O

I/O

PAD[4]

PAD[3]

AVC_SCLK Data I/Os

AVC

_

DATAI

AVC_CS

Chip select output that enables/disables a

serial configuration device.

Dedicated configuration data input pin

Dedicated configuration control input

Analog power for PLL1

Dedicated global clock input

Analog ground for PLL1

Output that drives low when device configu-

ration is complete.

Active-low chip enable

Dedicated mode select control pins that set

the configuration mode for the device.

Clock input (PS mode) or output (AS mode)

Active serial data output from the Cyclone device

I/O supply voltage pin for bank 1

Ground

P48V[8]

P48V[7]

P48V[6]

P48V[5]

P48V[4]

Data I/Os

P48V[3]

DA4358_CS

DA4382_CS

DA_CDTI

DA_CCLK

Ground

I/O supply voltage pin for bank 4

Ground

Internal logic array voltage supply pin

CLK18M

P48V[1]

PAD[1]

P48V[2]

PAD[2]

Data I/Os

Analog

_

MUTE

DSP

_

MUTE

/

DAC1

_

MUTE

/

DAC2

_

MUTE

MUTE_REQ

MUTE_OFF

Ground

Internal logic array voltage supply pin

Ground

I/O supply voltage pin for bank 4

EN[1]

EN[2] Data I/Os

EN[3]

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

IO

IO

IO

IO

IO

IO

IO

IO

GND

VCCIO3

CONF

_

DONE

nSTATUS

TCK

TMS

TDO

IO

CLK2

TDI

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

VCCIO2

GND

VCCINT

GND

IO

IO

IO

IO

IO

IO

IO

IO

IO

VCCINT

GND

VCCIO2

GND

IO

IO

IO

IO

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

-

I/O

-

-

I

I

O

I/O

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

-

-

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

-

-

I/O

-

I/O

I/O

I/O

I/O

EN[4]

MMD[7]

MMD[6]

MMD[5]

Data I/Os

MMD[4]

MMD[3]

MMD[2]

MMD[1]

Ground

I/O supply voltage pin for bank 3

Dedicated configuration status pin

Dedicated JTAG input pin

Dedicated JTAG output pin

MMD[0]

Dedicated global clock input

Dedicated JTAG input pin

CD60RD

CS61WR

CS62WR

CS63WR

MMA[1]

MIRQ

Data I/Os

MCI_SIRQ

DICE

_

IRQO

DA_MUTE

DICE

_

MUTE

AES

_

MUTE

/

WCK

_

MUTE

FW_MUTE

I/O supply voltage pin for bank 2

Ground

Internal logic array voltage supply pin

Ground

FS_CLK

TL1

DODATA[2]

DODATA[1]

DIDATA[2] Data I/Os

DIDATA[1]

DSAI_DO

DSAI_DI

DSAI_Fs

Internal logic array voltage supply pin

Ground

I/O supply voltage pin for bank 2

Ground

PAD[8]

PAD[7]

Data I/Os

PAD[6]

PAD[5]

EP1C3T100C8N (X5691A00) FPGA

DM: IC123

15

MR816CSX/MR816X

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

S1

S2

S3

S4

S5

VREF+

VDD

OSC2

OSC1

VSS

XI

XO

MMOD

RD0

RXD

D0

D1

D2

D3

D4

/RST

D5

D6

D7

D8

D9

S6

S7

S8

S9

S10

S11

I

I

I

I

I

-

-

O

I

-

I

O

I

O

I

O

O

O

O

O

I

O

O

O

O

O

I

I

I

I

I

I

Switch matrix data

Power supply (+5V, analog)

Power supply (+5V)

Crystal oscillator (8MHz)

Crystal oscillator (8MHz)

Ground

Not used

Not used

Memory mode select (Grounded)

Rotary encoder data

MIDI receive data

LED and switch drive data

Reset

LED and switch drive data

Switch matrix data

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

S12

S13

S14

TXD

S15

S16

S17

S18

L16

L17

L18

L19

L8

L9

L10

L11

L12

L13

L14

L15

L7

L6

L5

L4

L3

L2

L1

L0

VREF

AD0

AD1

S0

I

I

I

O

I

I

I

I

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

-

I

I

I

Switch matrix data

MIDI transmit data

Switch matrix data

LED drive data

LED and switch drive data

Grounded

Analog input

Analog input

Switch matrix data

MN101C027YB (XS71120R) CPU

DM: IC150

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

LREQ

SYSCLK

CNA

CTL0

CTL1

D0

D1

D2

D3

D4

D5

D6

D7

PD

LPS

NC

DGND

DGND

C/LKON

PC0

PC1

PC2

ISO

CPS

DV

DD

DVDD

TESTM

SE

SM

AV

DD

AVDD

AGND

I

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

-

-

I/O

I

I

I

I

I

-

-

I

I

I

-

-

-

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

AGND

TPB0–

TPB0+

TPA0–

TPA0+

TPBIAS0

AGND

R0

R1

AVDD

TPB1–

TPB1+

TPA1–

TPA1+

TPBIAS1

AGND

AGND

AGND

AV

DD

AVDD

RESET

FILTER0

FILTER1

PLLV

DD

PLLGND

PLLGND

XI

XO

DV

DD

DVDD

DGND

DGND

-

I/O

I/O

I/O

I/O

I/O

-

-

-

-

I/O

I/O

I/O

I/O

I/O

-

-

-

-

-

I

I/O

I/O

-

-

-

-

-

-

-

-

-

LLC request input

System clock output

Cable-not-active output

Control I/Os

Data I/Os

Power-down input

Link power status input

No connection

Digital ground

Bus manager contender programming input and link-on output

Power class programming inputs

Link interface isolation control input

Cable power status input

Digital power supply

Test control input

Test control input

Test control input

Analog power supply

Analog ground

Analog ground

Twisted-pair cable B differential signal

Twisted-pair cable A differential signal

Twisted-pair bias output

Analog ground

Current setting resistor

Analog power supply

Twisted-pair cable B differential signal

Twisted-pair cable A differential signal

Twisted-pair bias output

Analog ground

Analog power supply

Logic reset input

PLL filter

PLL power supply

PLL ground

Crystal oscillator inputs

Digital power supply

Digital ground

TSB41AB2PAP

(XZ665A00) PHY

DM: IC101

MR816CSX/MR816X

16

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

OUTER

NO.

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

C1

C2

C3

C4

C5

C6

C7

C8

C9

C10

C11

C12

C13

C14

C15

C16

C17

C18

C19

C20

D1

D2

D3

D4

D5

D6

D7

D8

VSS3OP

SRAM_WE

GPIO4/SRAM_READY

I2C_CLK

UART0_TX

TRST

TDI

SCMO

RESET

TCB[6]

TCA[6]

VDD3OP

VSS3I

VDD3OP

TCB[1]

TCA[0]

REFI

I2S_RX0_D3

I2S_RX0_BICK

I2S_RX0_MCK

D0

SRAM_BS[1]

SRAM_BS[0]

CS0

UART1_RX

VDD1IH

TDO

TMS

PLLE

VDD3OP

TCA[5]

TCB[4]

TCB[3]

TCB[2]

TCA[1]

FS32

I2S_RX0_D0

I2S_RX0_LRCK

I2S_TX0_D3

I2S_TX0_D1

D5

D1

SRAM_OE

CS3/EN4_B/GPIO6

I2C_DATA

UART1_TX

VSS3I

TCK

NLIG

TCA[7]

TCB[5]

TCA[4]

TCA[3]

TCA[2]

TCB[0]

REFO

I2S_RX0_D1

I2S_TX0_D2

I2S_TX0_D0

GPIO7/ I2S_TX0_MCK

D6

D2

D3

VSS3OP

CS2/EN4_A/GPIO5

VDD3OP

UART0_RX

VSS3OP

–

O

I/O

I/O

O

I

I

I

I

O

O

–

–

–

O

O

I

I

O

O

I/O

O

O

O

I

–

O

I

I

–

O

O

O

O

O

O

I

O

O

O

I/O

I/O

O

I/O

I/O

O

–

I

I

O

O

O

O

O

O

O

I

O

O

I/O

I/O

I/O

I/O

–

I/O

–

I

–

I/O ground

SRAM write enable

General purpose I/O / SRAM ready (read enable)

I2C Clock

Serial output

JTAG - Test reset (active low)

JTAG - Test data in

Scan mode select

Reset - active low

Test pin

Test pin

I/O 3.3V

Core ground

I/O 3.3V

Test pin

I2S Receiver 0 Data (ch.6/7)

I2S Receiver 0 Bit clock

I2S Receiver 0 Master clock

Data bus

SRAM upper byte select

SRAM lower byte select

Chip select

Serial intput

Core 1.8V

JTAG - Test data out

JTAG - Test mode select

PLL enable

I/O 3.3V

Test pin

I2S Receiver 0 Data (ch.0/1)

I2S Receiver 0 Left/Right clock

I2S Transmitter 0 Data ch.6/7

I2S Transmitter 0 Data ch.2/3

Data bus

SRAM output enable

Chip select / Rotary encoder input / General purpose I/O

I2C Data

Serial output

Core ground

JTAG - Test clock

Ignore PLL no-lock before releasing reset, active high.

Test pin

I2S Receiver 0 Data (ch.2/3)

I2S Transmitter 0 Data ch.4/5

I2S Transmitter 0 Data ch.0/1

General purpose I/O / I2S Transmitter 0 Master clock

Data bus

I/O ground

Chip select / Rotary encoder input / General purpose I/O

I/O 3.3V

Serial intput

I/O ground

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

OUTER

NO.

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

E1

E2

E3

E4

E17

E18

E19

E20

F1

F2

F3

F4

F17

F18

F19

F20

G1

G2

G3

G4

G17

G18

G19

G20

H1

H2

H3

H4

H17

H18

H19

H20

J1

J2

J3

J4

J9

J10

J11

J12

J17

J18

J19

J20

K1

K2

K3

K4

K9

K10

K11

K12

K17

K18

K19

K20

TEMO

TCB[7]

VDD3OP

VDD1IH

VSS3OP

VDD3OP

VDD3OP

I2S_RX0_D2

VSS3OP

GPIO9/ I2S_TX0_LRCLK

VDD1IH

I2S_RX1_D1

D9

D8

D7

D4

GPIO8/I2S_TX0_BICK

VSS3I

I2S_RX1_D0

I2S_RX1_MCK

D13

D12

D10

VDD3OP

VDD3OP

I2S_RX1_LRCK

I2S_TX1_D1

I2S_TX1_LRCLK

VSS3I

D15

D14

D11

I2S_RX1_BICK

I2S_TX1_D0

I2S_TX1_BICK

I2S_TX1_MCK

A1

A0

VDD1IH

VSS3OP

VSS3OP

I2S_RX2_D1

I2S_RX2_D0

I2S_RX2_LRCK

A5

A4

A3

A2

VSS3OP

VSS3OP

VSS3OP

VSS3OP

I2S_RX2_BICK

I2S_RX2_MCK

I2S_TX2_D1

I2S_TX2_D0

A8

A6

A7

VDD3OP

VSS3OP

VSS3OP

VSS3OP

VSS3OP

GPIO12/I2S_TX2_LRCLK

GPIO11/I2S_TX2_BICK

GPIO10/I2S_TX2_MCK

HPX1

I

O

–

–

–

–

–

I

–

I/O

–

I

I/O

I/O

I/O

I/O

I/O

–

I

O

I/O

I/O

I/O

–

–

O

O

O

–

I/O

I/O

I/O

O

O

O

O

O

O

–

–

–

I

I

O

O

O

O

O

–

–

–

–

O

O

O

O

O

O

O

–

–

–

–

–

I/O

I/O

I/O

O

Test mode pin

Test pin

I/O 3.3V

Core 1.8V

I/O ground

I/O 3.3V

I2S Receiver 0 Data (ch.4/5)

I/O ground

General purpose I/O / I2S Transmitter 0 Left/Right clock

Core 1.8V

I2S Receiver 1 Data (ch.2/3)

Data bus

General purpose I/O / I2S Transmitter 0 Bit clock

Core ground

I2S Receiver 1 Data (ch.0/1)

I2S Receiver 1 Master clock

Data bus

I/O 3.3V

I2S Receiver 1 Left/Right clock

I2S Transmitter 1 Data ch.2/3

I2S Transmitter 1 Left/Right clock

Core ground

Data bus

I2S Receiver 1 Bit clock

I2S Transmitter 1 Data ch.0/1

I2S Transmitter 1 Bit clock

I2S Transmitter 1 Master clock

Address bus

Core 1.8V

I/O ground

I2S Receiver 2 Data (ch.2/3)

I2S Receiver 2 Data (ch.0/1)

I2S Receiver 2 Left/Right clock

Address bus

I/O ground

I2S Receiver 2 Bit clock

I2S Receiver 2 Master clock

I2S Transmitter 2 Data ch.2/3

I2S Transmitter 2 Data ch.0/1

Address bus

I/O 3.3V

I/O ground

General purpose I/O / I2S Transmitter 2 Left/Right clock

General purpose I/O / I2S Transmitter 2 Bit clock

General purpose I/O / I2S Transmitter 2 Master clock

GPIO(Z)

1394AV-L (X6893A00) DICEII

DM: IC103

17

MR816CSX/MR816X

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

OUTER

NO.

L1

L2

L3

L4

L9

L10

L11

L12

L17

L18

L19

L20

M1

M2

M3

M4

M9

M10

M11

M12

M17

M18

M19

M20

N1

N2

N3

N4

N17

N18

N19

N20

P1

P2

P3

P4

P17

P18

P19

P20

R1

R2

R3

R4

R17

R18

R19

R20

T1

T2

T3

T4

T17

T18

T19

T20

U1

U2

U3

U4

U5

U6

U7

U8

U9

U10

U11

U12

A9

A10

A11

A12

VSS3OP

VSS3OP

VSS3OP

VSS3OP

VDD3OP

HPX3

PLL_1V8 (HPLL1)

HPX2

A13

A14

A15

A16

VSS3OP

VSS3OP

VSS3OP

VSS3OP

FILTER_HPLL2

PLL_GND (HPLL1)

PLL_BULK (HPLL1)

FILTER_HPLL1

A17

A18

A19

VSS3OP

VSS3OP

PLL_GND (HPLL2)

PLL_BULK (HPLL2)

PLL_1V8 (HPLL2)

A20/CS7/EN1_A

A21/CS6/EN1_B

A23/CS4/EN2_B/GPO6

CLKO

VSS3I

PLL_BULK (CLK_CBL)

PLL_1V8 (CLK_DBL)

FILTER_CLK_DBL

A22/CS5/EN2_A

VSS3I

GPIO1/CLKE

VDD3OP

VDD3OP

XTAL1

VDD1IH

PLL_GND (CLK_DBL)

VDD1IH

RAS

SDRAM_WE

SDRAM_DQM1

DSAI_TX0

DSAI_TX3

VDD3OP

XTAL2

CAS

CS1

SDRAM_BNK0

VSS3OP

PHD5

VDD3OP

PHLP

VSS3OP

VD5/TDF_IFS0/U1_DSR/HFS1

VDD3OP

GPIO15/WCKO/TDF_OEM/U0_OUT2

FILTER_TDIF

O

O

O

O

–

–

–

–

–

I/O

–

O

O

O

O

O

–

–

–

–

A

–

–

A

O

O

O

–

–

–

–

–

I/O

I/O

I/O

O

–

–

–

A

I/O

–

I/O

–

–

I

–

–

–

O

O

O

O

O

–

O

O

O

O

–

I/O

–

O

–

I/O

–

I/O

A

Address bus

I/O ground

I/O 3.3V

GPIO

PLL 1.8V

GPIO(Z)

Address bus

I/O ground

JETPLL filter component connection

PLL ground

PLL bulk bias

JETPLL filter component connection

Address bus

I/O ground

PLL ground

PLL bulk bias

PLL 1.8V

Address bus / Chip select / Rotary encoder input

Address bus / Chip select / Rotary encoder input / General purpose

SDRAM interface AHB Bus clock

Core ground

PLL bulk bias

PLL 1.8V

Clock Doubler VCO filter component connection

Address bus / Chip select / Rotary encoder input

Core ground

General purpose I/O / SDRAM interface Clock enable

I/O 3.3V

XTAL for clock doubler/power manager/LLC

Core 1.8V

PLL ground

Core 1.8V

SDRAM interface Row address strobe

SDRAM interface Write enable

SDRAM interface Upper byte mask

DSAI Transmitter 0 data line

DSAI Transmitter 3 data line

I/O 3.3V

XTAL for clock doubler/power manager/LLC

SDRAM interface Column address strobe

Chip select

SDRAM interface Bank addsess

I/O ground

PHY tristable data line bit 5

I/O 3.3V

Link power status. Pulsing if isolation barrier present.

I/O ground

Video interface - Data byte bit 5 / TDIF sample rate 0 input / Data set ready UART status input / 512fs base rate clock

I/O 3.3V

General purpose I/O / Word clock out / TDIF emphasis output / UART control programmable output 2 output

TDIF Receiver VCO filter component connection

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

241

242

243

244

245

246

247

248

249

250

251

252

253

254

255

256

257

258

259

260

261

262

263

264

265

266

267

268

269

270

271

272

OUTER

NO.

U13

U14

U15

U16

U17

U18

U19

U20

V1

V2

V3

V4

V5

V6

V7

V8

V9

V10

V11

V12

V13

V14

V15

V16

V17

V18

V19

V20

W1

W2

W3

W4

W5

W6

W7

W8

W9

W10

W11

W12

W13

W14

W15

W16

W17

W18

W19

W20

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

Y9

Y10

Y11

Y12

Y13

Y14

Y15

Y16

Y17

Y18

Y19

Y20

VSS3OP

AES_RX2

VDD3OP

DSAI_RX1

VSS3OP

DSAI_SYNCD

DSAI_CKD

DSAI_TX2

SDRAM_DQM0

SDRAM_BNK1

EN3_B/GPIO3/SDRAM_BNK3

PHD4

PHCT0

PHLR

VDD1IH

VD2/TDF_I2/U0_DCD

VD6/TDF_IFS1/U1_DCD/HFS2

VCLK/TDF_O2/U1_OUT1

GPIO14/WCKI/TDF_OFS1/U0_OUT1

PLL_1V8 (AES,ADAT,TDIF)

PLL_GND (AES,ADAT,TDIF)

EXT_512BR

AES_RX3

AES_TX2

DSAI_RX2

DSAI_SYNCA

DSAI_SYNCC

DSAI_TX1

EN3_A /GPIO2/SDRAM_BNK2

SCLK

PHD1

PHD3

PHCT1

PHLO

VD0/TDF_I0/U0_CTS

VD3/TDF_I3/U0_RI

VD7/TDF_IEM/U1_RI

VRDY/TDF_O1/U1_RTS

GPIO13/BLKS/TDF_OFS0/U0_RTS

VSS3I

FILTER_AES

OPTI

AES_RX0

AES_TX0

AES_TX3

DSAI_RX3

DSAI_CKB

DSAI_CKC

PHD0

PHD2

PHD6

PHD7

PHDI

VSS3I

VD1/TDF_I1/U0_DSR

VD4/TDF_ILR/U1_CTS

VFSYNC/TDF_O0/U1_DTS

VEND_DB/TDF_O3/U1_OUT2

VVALID/TDF_OLR/U0_DTS

VDD1IH

FILTER_ADAT

OPTP

EXT_FBR

AES_RX1

AES_TX1

DSAI_RX0

DSAI_CKA

DSAI_SYNCB

–

I

–

I

–

I/O

I/O

O

O

O

I/O

I/O

I/O

O

–

I/O

I/O

I/O

I/O

–

–

I/O

I

O

I

I/O

I/O

O

I/O

I

I/O

I/O

I/O

I

I/O

I/O

I/O

I/O

I/O

–

A

I

I

O

O

I

I/O

I/O

I/O

I/O

I/O

I/O

I

–

I/O

I/O

I/O

I/O

I/O

–

A

O

I/O

1

O

I

I/O

I/O

I/O ground

AES3 Receiver ch4/5

I/O 3.3V

DSAI Receiver 1 data line

I/O ground

DSAI Sync D

DSAI Clock D

DSAI Transmitter 2 data line

SDRAM interface Lower byte mask

SDRAM interface Bank addsess

Rotary encoder input / General purpose I/O / SDRAM interface Bank addsess

PHY tristable data line bit 4

PHY tristable control line bit 0

Serial request output from S-LINK(Z)

Core 1.8V

Video interface - Data byte bit 2 / TDIF audio data input 3 / Data carrier detect UART status input

Video interface - Data byte bit 6 / TDIF sample rate 1 input / Data carrier detect UART status input / 512fs base rate clock

Video interface - Video Clock / TDIF audio data output 3 / UART control programmable output 1 output

General purpose I/O / Word clock in / TDIF sample rate 1 output / UART control programmable output 1 output

PLL 1.8V

PLL ground

External 512 x base rate clock

AES3 Receiver ch.6/7

AES3 Transmitter ch.4/5

DSAI Receiver 2 data line

DSAI Sync A

DSAI Sync C

DSAI Transmitter 1 data line

Rotary encoder input / General purpose I/O / SDRAM interface Bank addsess

49.152MHz PHY Clock input

PHY tristable data line bit 1

PHY tristable data line bit 3

PHY tristable control line bit 1

Link on indication from PHY. Pulsing when asserted.

Video interface - Data byte bit 0 / TDIF audio data input 1 / Clear to send UART status input

Video interface - Data byte bit 3 / TDIF audio data input 4 / Ring indicator UART status input

Video interface - Data byte bit 7 / TDIF emphasis input / Ring indicator UART status input

Video interface - Video ready signal / TDIF audio data output 2 / UART control request to send output

General purpose I/O / Block sync input/output signal / TDIF sample rate 0 output / UART control request to send output

Core ground

AES Receiver filter component connection

Optical audio in

AES3 Receiver ch.0/1

AES3 Transmitter ch.0/1

AES3 Transmitter ch.6/7

DSAI Receiver 3 data line

DSAI Clock B

DSAI Clock C

PHY tristable data line bit 0

PHY tristable data line bit 2

PHY tristable data line bit 6

PHY tristable data line bit 7

A high indicates isolation barrier is not present.

Core ground

Video interface - Data byte bit 1 / TDIF audio data input 2 / Data set ready UART status input

Video interface - Data byte bit 4 / TDIF left right clock input / Clear to send UART status input

Video interface - Video sync signal / TDIF audio data output 1 / UART control data terminalready output

Video interface - End of Data block / TDIF audio data output 4 / UART control programmable output 1 output

Video interface - Video data valid / TDIF left right clock output / UART control data terminal ready output

Core 1.8V

ADAT Receiver filter component connection

Optical audio out

External 1fs base rate clock

AES3 Receiver ch.2/3

AES3 Transmitter ch.2/3

DSAI Receiver 0 data line

DSAI Clock A

DSAI Sync B

MR816CSX/MR816X

18

DM: IC131, 132

PIN

NO.

I/O

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

PIN

NO.

I/O

NAME

WAITN

IRQN_OUT

VSS

VDDE

SCANSW[4]

SCANSW[3]

SCANSW[2]

SCANSW[1]

SCANSW[0]

VSS

VDDI

ADVDD

ADVSS

VRL

VREF

ANPORT[3]

ANPORT[2]

ANPORT[1]

ANPORT[0]

VRH

VDDE

IRQN_IN

ARMSTOP

VSS

XI

VSS

VDDI

XO

TESTN

VDDE

PLVDD

PLVSS

PLLBPN

VDDI

ACLK

AFRM

ADIR

VSS

ADAT[0]

ADAT[1]

ADAT[2]

ADAT[3]

VDDE

ADAT[4]

ADAT[5]

ADAT[6]

ADAT[7]

ADAT[8]

ADAT[9]

VSS

ADAT1[0]

ADAT[11]

ADAT[12]

ADAT[13]

ADAT[14]

ADAT[15]

DITO

SYSCLK

SYO

VSS

VDDE

BCLK

WCLK0

SDO[0]

SDO[1]

SDO[2]

SDO[3]

SDO[4]

SDO[5]

SDO[6]

SDO[7]

VSS

VDDI

MUTEN

SDI[0]

SDI[1]

SDI[2]

SDI[3]

VDDI

SDI[4]

SDI[5]

SDI[6]

VDDE

EXCLK

VSS

VDDI

SDI[7]

SDI[8]

SDI[9]

SDI[10]

SDI[11]

SYI

VPD

VSS

RCLKI

VSS

VDDE

RCLK

VSS

RDN

WRN

UBN

LBN

VDDE

Wait for external CPU

Output of interrupt information

VSS

VDDE +3.3V

Scan control

VSS

VDDI +1.8V

ADVDD 3.3V

ADVSS

ADC reference voltage

ADC reference voltage

ADC analog input

ADC reference voltage

VDDE +3.3V

Interrupt input

ARM stop

VSS

Crystal oscillator(input)

VSS

VDDI +1.8V

Crystal oscillator(output)

Test pin

VDDE +3.3V

PLVDD +1.8V

PLVSS

Switch of PLL and XI

VDDI +1.8V

ABUS clock

ABUS frame

ABUS directon

VSS

ABUS data bus

VDDE +3.3V

ABUS data bus

VSS

ABUS data bus

DIT output

System clock

External synchronization

VSS

VDDE +3.3V

Bit clock of SDI, SDO

Word clock of SDI, SDO

Serial audio output

VSS

VDDI +1.8V

Audio mute

Serial audio input

VDDI +1.8V

Serial audio input

VDDE +3.3V

External synchronization clock

VSS

VDDI +1.8V

Serial audio input

External synchronization input

Test pin

VSS

SDRAM clock

VSS

VDDE +3.3V

SDRAM clock

VSS

External memory read

External memory write

RAM enable(Upper Byte)

RAM enable(Lower Byte)

VDDE +3.3V

Data bus(ARM,DSP -> memory)

Data bus(ARM,DSP -> memory)

VSS

Data bus(ARM,DSP -> memory)

VDDE +3.3V

Data bus(ARM,DSP -> memory)

VSS

Data bus(ARM,DSP -> memory)

VDDI +1.8V

Data bus(ARM,DSP -> memory)

Memory addres bus

VDDE +3.3V

VSS

VDDI +1.8V

Memory addres bus

VDDI +1.8V

Memory addres bus

VSS

Memory addres bus

VDDE +3.3V

Memory addres bus

Chip Select

VSS

Chip Select

External Address bus / GPIO

VSS

VDDE +3.3V

External Address bus / GPIO

External chip select

External read

External write

External Data bus / GPIO

VSS

VDDI +1.8V

External Data bus / GPIO

VDDI +1.8V

External Data bus / GPIO

VSS

VDDI +1.8V

External Data bus / GPIO

VDDE +3.3V

JTAG clock

JTAG mode

JTAG reset

VSS

VDDE +3.3V

Initial clear

JTAG input

JTAG output

Serial output 0

Serial input 0

Serial output 1

Serial input 1

O

O

-

-

O

O

O

O

O

-

-

-

-

I

I

I

I

I

I

I

-

I

I

-

I

-

-

I/O

I

-

-

-

I

-

I/O

I/O

O

-

I/O

I/O

I/O

I/O

-

I/O

I/O

I/O

I/O

I/O

I/O

-

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

-

-

O

O

O

O

O

O

O

O

O

O

-

-

I

I

I

I

I

-

I

I

I

-

I

-

-

I

I

I

I

I

I

I

-

I

-

-

O

-

O

O

O

O

-

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

MD[7]

MD[6]

VSS

MD[5]

MD[4]

MD[3]

MD[2]

MD[1]

MD[0]

VDDE

MD[15]

MD[14]

MD[13]

MD[12]

VSS

MD[11]

MD[10]

MD[9]

VDDI

MD[8]

MA[12]

MA[10]

MA[9]

MA[8]

VDDE

VSS

VDDI

MA[7]

MA[6]

MA[5]

MA[13]

MA[14]

MA[11]

VDDI

MA[1]

MA[2]

MA[3]

VSS

MA[4]

MA[18]

MA[19]

MA[17]

VDDE

MA[16]

MA[15]

MA[20]

CS0N

CS2N

CS3N

VSS

CS4N

EA[1]

EA[2]

EA[3]

EA[4]

EA[5]

EA[6]

EA[7]

EA[8]

VSS

VDDE

EA[9]

EA[10]

EA[11]

EA[12]

EA[13]

EA[14]

ECSN

ERDN

EWRN

ED[0]

VSS

VDDI

ED[1]

ED[2]

ED[3]

ED[4]

ED[5]

VDDI

ED[6]

ED[7]

ED[8]

ED[9]

ED[10]

VSS

VDDI

ED[11]

ED[12]

ED[13]

ED[14]

ED[15]

VDDE

TCK

TMS

TRST

VSS

VDDE

ICN

TDI

TDO

TXD0

RXD0

TXD1

RXD1

I/O

I/O

-

I/O

I/O

I/O

I/O

I/O

I/O

-

I/O

I/O

I/O

I/O

-

I/O

I/O

I/O

-

I/O

O

O

O

O

-

-

-

O

O

O

O

O

O

-

O

O

O

-

O

O

O

O

-

O

O

O

O

O

O

-

O

I

I

I

I

I

I

I

I

-

-

I

I

I

I

I

I

I

I

I

I/O

-

-

I/O

I/O

I/O

I/O

I/O

-

I/O

I/O

I/O

I/O

I/O

-

-

I/O

I/O

I/O

I/O

I/O

-

I

I

I

-

-

I

I

O

O

I

O

I

FUNCTION FUNCTION

MB87S1280 (X6363A00) SSP1 (MAIN/SUB)

19

MR816CSX/MR816X

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

CLKI

CLKO

V

DD

SCANENB

ATPGENB

VSS

PLLTEST

PLLRES

PLLV

SS

MVDD

PLLVSS

AVDD

CHG0

LPV

SS

VSS

MIRQ

MCS

MWR

MRD

MA

VDD

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

VSS

MD8

VDD

MD9

MD10

MD11

MD12

MD13

MD14

MD15

VSS

I

O

-

I/O

I/O

-

I

I

-

-

-

-

-

-

I/O

I

I

I

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

-

I/O

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

-

Clock

Power supply

Scan enable

Ground

Tes t

Reset

Ground

Power supply

Ground

Analog power supply

Ground

Interrupt request

Control port

Write

Read

Power supply

DRAM data bus

Ground

DRAM data bus

Power supply

DRAM data bus

Ground

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

VDD

RESET

VSS

OUT4

OUT3

INP2

INP1

INP0

TESTENB

VSS

OSCO

V

DD

OSCI

V

SS

SIRQ

SCS

SWR

SRD

SA

VSS

VDD

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

VSS

SD8

VDD

SD9

SD10

SD11

SD12

SD13

SD14

SD15

VSS

-

I

-

O

O

I

I

I

I/O

-

-

-

I/O

I

I

I

-

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

-

I/O

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

-

Power supply

Reset

Ground

Output

Input

Test enable

Ground

Power supply

Ground

Interrupt request

Control port

Write

Read

Ground

Power supply

Serial data

Ground

Serial data

Power supply

Serial data

Ground

DM: IC111

S1L50553F21Y000 (X4195A0R) MCI (Gate Array)

AK5385BVF-E2 (X5364B00) ADC (Analog to Digital Converter)

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

VREFL

AVSS

VCOM

LIN+

LIN–

CKS0

DVDD

DVSS

OVF

PDN

DIF

M/S

LRCK

BICK

I

–

O

I

I

I

–

–

O

I

I

I

I/O

I/O

Lch voltage reference input

Analog ground

Common voltage output

Lch analog positive input

Lch analog negative input

Master clock select 0

Digital power supply (3.0 - 5.25 V)

Digital ground

Analog input overflow detect

Power down mode

Audio interface format

Master / Slave mode

Output channel clock

Audio serial data clock

15

16

17

18

19

20

21

22

23

24

25

26

27

28

SDTO

CKS1

MCLK

DFS0

HPFE

DFS1

BVSS

AVSS

AVDD

RIN–

RIN+

TEST

AVSS

VREFR

O

I

I

I

I

I

–

–

–

I

I

I

–

I

Audio serial date output

Master clock select 1

Master clock input

Sampling speed select 0

High pass filter enable

Sampling speed select 1

Substrate ground

Analog ground

Analog power supply (4.75 - 5.25 V)

Rch analog negative input

Rch analog positive input

Test pin

Analog ground

Rch voltage reference input

DM: IC704, 709, 710, 712

MR816CSX/MR816X

20

PIN

NO.

I/O FUNCTION

NAME

PIN

NO.

I/O FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

LOUT1-

LOUT1+

DZF3

DZF2

DZF1

CAD0

ACKSN

PDN

BICK

MCLK

DVDD

DVSS

SDTI4

SDTI1

SDTI2

SDTI3

LRCK

I2C

CCLK

/

SCL

CDTI

/

SDA

CSN

/

CAD1

O

O

O

O

O

I

I

I

I

I

-

-

I

I

I

I

I

I

I

I/O

I

DAC1 Lch Negative Analog Output Pin

DAC1 Lch Positive Analog Output Pin

Zero Input Detect 3 Pin

Zero Input Detect 2 Pin

Zero Input Detect 1 Pin

Chip Address 0 Pin

Auto Setting Mode Disable Pin (Pull-down Pin)

“L”: Auto Setting Mode, “H”: Manual Setting Mode

Power-Down Mode Pin

When at “L”, the AK4358 is in the power-down mode

and is held in reset.

Audio Serial Data Clock Pin

Master Clock Input Pin

An external TTL clock should be input on this pin.

Digital Power Supply Pin, +4.75 +5.25V

Digital Ground Pin

DAC4 Audio Serial Data Input Pin

DAC1 Audio Serial Data Input Pin

DAC2 Audio Serial Data Input Pin

DAC3 Audio Serial Data Input Pin

L/R Clock Pin

Control Mode Select Pin

“L”: 3-wire Serial, “H”: I2C Bus

Control Data Clock Pin

I2C = “L”: CCLK (3-wire Serial), I2C = “H”: SCL (I2C Bus)

Control Data Input Pin

I2C = “L”: CDTI (3-wire Serial), I2C = “H”: SDA (I2C Bus)

Chip Select Pin

I2C = “L”: CSN (3-wire Serial), I2C = “H”: CAD1 (I2C Bus)

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

DCLK

DSDL4

DSDR4

DSDL1

DSDR1

DSDL2

DSDR2

DSDL3

DSDR3

DIF0

ROUT4-

ROUT4+

VREFH

AVDD

AVSS

LOUT4-

LOUT4+

ROUT3-

ROUT3+

LOUT3-

LOUT3+

ROUT2-

ROUT2+

LOUT2-

LOUT2+

ROUT1-

ROUT1+

I

I

I

I

I

I

I

I

I

I

O

O

I

-

-

O

O

O

O

O

O

O

O

O

O

O

O

DSD Clock Pin

DAC4 DSD Lch Data Input Pin

DAC4 DSD Rch Data Input Pin

DAC1 DSD Lch Data Input Pin

DAC1 DSD Rch Data Input Pin

DAC2 DSD Lch Data Input Pin

DAC2 DSD Rch Data Input Pin

DAC3 DSD Lch Data Input Pin

DAC3 DSD Rch Data Input Pin

Audio Data Interface Format 0 Pin

DAC4 Rch Negative Analog Output Pin

DAC4 Rch Positive Analog Output Pin

Positive Voltage Reference Input Pin

Analog Power Supply Pin, +4.75 +5.25V

Analog Ground Pin

DAC4 Lch Negative Analog Output Pin

DAC4 Lch Positive Analog Output Pin

DAC3 Rch Negative Analog Output Pin

DAC3 Rch Positive Analog Output Pin

DAC3 Lch Negative Analog Output Pin

DAC3 Lch Positive Analog Output Pin

DAC2 Rch Negative Analog Output Pin

DAC2 Rch Positive Analog Output Pin

DAC2 Lch Negative Analog Output Pin

DAC2 Lch Positive Analog Output Pin

DAC1 Rch Negative Analog Output Pin

DAC1 Rch Positive Analog Output Pin

AK4358VQ (X4289A00) DAC (Digital to Analog Converter)

DM: IC751

PIN

NO.

I/O FUNCTIONNAME

PIN

NO.

I/O

FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

AVSS

AVDD

IN1

IN2

IN3

IN4

IN5

IN6

IN7

AVDD

AVSS

REF7B

REF7A

REF6B

REF6A

REF5B

REF5A

REF4A

REF4B

REF3A

REF3B

REF2A

-

-

I

I

I

I

I

I

I

-

-

I

I

I

I

I

I

I

I

I

I

I

Minus power supply for analog (-6.0V Typ.)

Plus power supply for analog (+6.0V Typ.)

ch1 analog input

ch2 analog input

ch3 analog input

ch4 analog input

ch5 analog input

ch6 analog input

ch7 analog input

Plus power supply for analog (+6.0V Typ.)

Minus power supply for analog (-6.0V Typ.)

ch7 analog reference voltage input 7B

Connect to ground directly.

ch7 analog reference voltage input 7A

Connect to ground through 33F.

ch6 analog reference voltage input 6B

Connect to ground directly.

ch6 analog reference voltage input 6A

Connect to ground through 33F.

ch5 analog reference voltage input 5B

Connect to ground directly.

ch5 analog reference voltage input 5A

Connect to ground through 33F.

ch4 analog reference voltage input 4A

Connect to ground through 33F.

ch4 analog reference voltage input 4B

Connect to ground directly.

ch3 analog reference voltage input 3A

Connect to ground through 33F.

ch3 analog reference voltage input 3B

Connect to ground directly.

ch2 analog reference voltage input 2A

Connect to ground through 33F.

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

REF2B

REF1A

REF1B

NC

NC

OUT7

OUT6

OUT5

OUT4

OUT3

OUT2

OUT1

NC

NC

AVSS

ZCEN1

ZCEN2

CSN

SDATAI

SCLK

SDATAO

TE2

TE1

DGND

REF

AVSS

I

I

I

-

-

O

O

O

O

O

O

O

-

-

-

I

I

I

I

I

O

I

I

-

O

-

ch2 analog reference voltage input 2B

Connect to ground directly.

ch1 analog reference voltage input 1A

Connect to ground through 33F.

ch1 analog reference voltage input 1B

Connect to ground directly.

Non connection or connect to ground.

Non connection or connect to ground.

ch7 analog output

ch6 analog output

ch5 analog output

ch4 analog output

ch3 analog output

ch2 analog output

ch1 analog output

Non connection or connect to ground.

Non connection or connect to ground.

Minus power supply for analog (-6.0V Typ.)

Zero-cross control input 1

Zero-cross control input 2.

Chip select input

Serial data input

Serial clock input

Serial data output

Serial data are outputted from this terminal when

CSN pin is "L" level. This terminal becomes

high-impedance state when CSN pin is "H".

Test terminal

Non connection or connect to DGND terminal.

Test terminal

Non connection or connect to DGND terminal.

Digital ground

Reference voltage output for digital

Minus power supply for analog (-6.0V Typ.)

YAC523-VZ (X4325A00) EVR2 (Electric Variable Resistance 2)

DM: IC814

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

ページが読み込まれています...

-

1

1

-

2

2

-

3

3

-

4

4

-

5

5

-

6

6

-

7

7

-

8

8

-

9

9

-

10

10

-

11

11

-

12

12

-

13

13

-

14

14

-

15

15

-

16

16

-

17

17

-

18

18

-

19

19

-

20

20

-

21

21

-

22

22

-

23

23

-

24

24

-

25

25

-

26

26

-

27

27

-

28

28

-

29

29

-

30

30

-

31

31

-

32

32

-

33

33

-

34

34

-

35

35

-

36

36

-

37

37

-

38

38

-

39

39

-

40

40

-

41

41

-

42

42

-

43

43

-

44

44

-

45

45

-

46

46

-

47

47

-

48

48

-

49

49

-

50

50

-

51

51

-

52

52

-

53

53

-

54

54

-

55

55

-

56

56

-

57

57

-

58

58

-

59

59

-

60

60

-

61

61

-

62

62

-

63

63

-

64

64

-

65

65

-

66

66

-

67

67

-

68

68

-

69

69

-

70

70

-

71

71

-

72

72

-

73

73

-

74

74

-

75

75

-

76

76

-

77

77

-

78

78

-

79

79

-

80

80

-

81

81

-

82

82

-

83

83

-

84

84

-

85

85

-

86

86

-

87

87

-

88

88

-

89

89

-

90

90

-

91

91

-

92

92

-

93

93

-

94

94

-

95

95

-

96

96

-

97

97

-

98

98

-

99

99

-

100

100

-

101

101

-

102

102

-

103

103

-

104

104

-

105

105

-

106

106

-

107

107